LICENSE >>

<< Launch Mail

News Index

2002

Jan Feb Mar

Apr May Jun

Jul Aug Sep

2001

Jan Feb Mar

Apr May Jun

Jul Aug Sep

Oct Nov Dec

2000

Apr Aug Sep

Oct Nov Dec

Links

Fpga-cpu List

Usenet Posts

Site News

Papers

Teaching

Resources

Glossary

Gray Research

GR CPUs

XSOC

Launch Mail

Circuit Cellar

LICENSE

README

XSOC News

XSOC Talk

Issues

xr16

XSOC 2.0

XSOC2 Log

CNets

CNets Log

[updated: 03/07/01:]

Here are the original draft versions of the articles:

xsoc-series-drafts.pdf.

These drafts have better schematics, and a more conversational style.

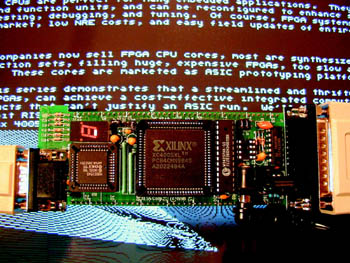

The articles present the design and implemention of the XSOC System-on-a-Chip, including the new xr16 pipelined RISC processor core, on-chip bus, bus/memory controller, and integrated peripherals (parallel port, bilevel VGA controller), all in a single Xilinx XC4005XL FPGA, and also describe a port of the lcc4.1 retargetable C compiler, an assembler, simulator, and demos.

Theme:

"Several companies sell FPGA CPU cores, but most are synthesized implementations of existing instruction sets, filling huge, expensive FPGAs, and are too slow and too costly for production use. These cores are marketed as ASIC prototyping platforms.""In contrast, this article shows how a streamlined and thrifty CPU design, optimized for FPGAs, can achieve a cost-effective integrated computer system, even for low-volume products that can't justify an ASIC run."

Copyright © 2000-2002, Gray Research LLC. All rights reserved.

Last updated: Mar 09 2001